# Die Backside Surface Subtractive Method for Thin Die Application

Bryan Christian S. Bacquian

Central Engineering and Development – NPI, Back-End Manufacturing & Technology, STMicroelectronics, Inc. Calamba City, Laguna, Philippines 4027

**Abstract**— Advance and Thinner Packages are becoming eminent on the semiconductor field, in order to cater the demanding needs of thinner electronics devices. However, thinner package architectures does possess several assembly problems such as die crack. Die crack is very prone since the wafers are grinded up to thicknesses of 100um and below. Several actions were also present to mitigate this die crack phenomenon. However, the paper discusses subtractive method during wafer preparation process in order to reduce the contact area of the die on the mounting tape, which can cause cracking during die pick up step of die attach process.

*Keywords*— *Die Crak; Die Backside; Wafer Backgrind; Subtractive method; semiconductor package; process solutions.*

## I. INTRODUCTION

Integrated Circuit manufacturers were challenged to develop thinner packages that can support the emerging electronics technology. Advanced integrated circuit manufacturers has called the need of wafer thinning process as a technology enabler for electronics packages used for memory cards and multi-chip packages [1]. Wafer back grinding is the critical process enabler for this packages. Wafers were grinded up to 100um and even thinner. The process includes three critical process steps, coarse, fine and stress relief, which ensures that the die has enough strength to withstand package stresses. The paper introduces an innovative process solution to improve the die strength during die pick-up step at die attach process, specifically for thin packages.

Die Attach process is the process, which involves binding the silicon die into the carrier via an epoxy adhesive. However, during the process, several problems may occur due to complexity of the process such as picking up of the dies from the wafer frame. Figure 1 shows die crack phenomena merely present on the center of the die and cause by an external force. Several causes, such as process and material characteristics can result to this defect manifestation.

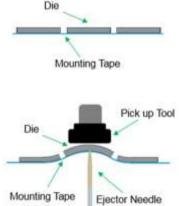

One of the problem was the die strength cause by high stress induced towards the die. Silicon die strength is an important parameter to ensure the packaging reliability under stringent conditions [2]. The characteristics known was Surface roughness that is known to influence the characteristics of a grinded work piece which focus on resistance to failure [3]. However, the two characteristics was already optimized and yet the problem has not yet mitigated. According to WL. Chin, et al. [4], crack die will not only happen during wafer preparation process thus it can happen across all process steps of the integrated circuit assembly. Figure 2 shows the die crack phenomena is happening during the die pick up step.

Fig. 2. Die Attach Pick Mechanism using standard process

The picking and placing of thin dies from wafer mounting tape is extremely difficult. Several actions like slowing the pick time in order to pick slowly the die [5]. However, the problem the die will perfectly detach from the tape if the problem is adhesion. The paper will discuss the introduction of a new innovative process that can reduce the contact area of the die with respect to tape thus will reduce the detach area and latter will reduce the die stress during die pick-up.

#### II. PROCESS SOLUTION

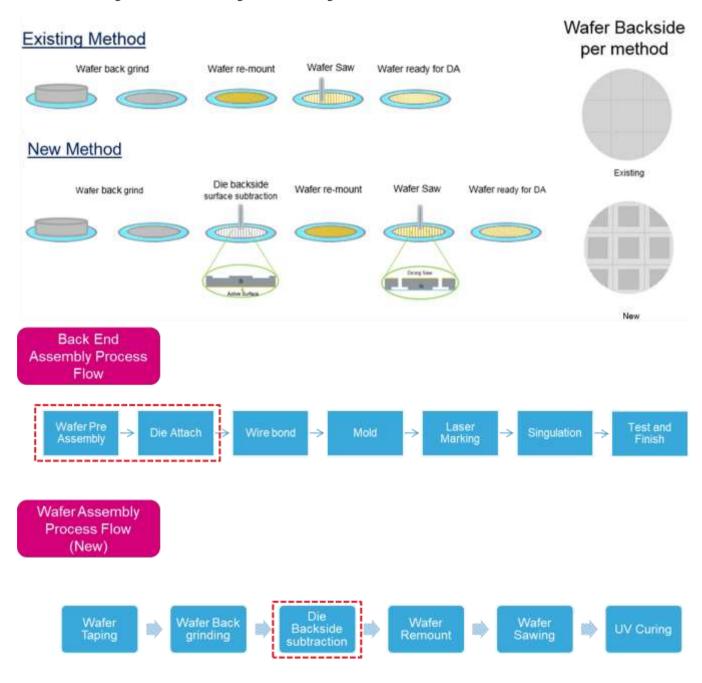

The innovative process solution offers die crack defect reduction initiative. As shown on Figure 3, the existing method of wafer preparation, the standard process involves the wafer backgrind process, wherein the thinning is happening then mounted on a wafer frame and a mounting tape. Then after followed by wader sawing and lastly Die Attach. Since the die backside is in full contact towards the tape, which has high adhesion strength, the pick force to be exerted by the die attach process may be higher than the die strength, therefore

die crack will definitely occur. The proposed solution is the application of subtractive method, as shown on Figure 3 New Method, die backside or silicon area will be reduced to 50% or less by means of reducing the surface area of wafer backside with depth of 10 um (as shown on the left of Figure 3). This method will be performed using a wafer-sawing machine. In addition, the critical process will be the die Backside surface subtraction, wherein a grinding wheel type material (like a dicing saw) will be the one to grind 10um from the surface. Infrared camera will guide the wafer-sawing machine during

the process since standard sawing machine is not capable of aligning an object without unique pattern, in this case is a full silicon die backside. With the area of die with direct contact on mounting tape is reduce, adhesion strength of die to mounting tape is then reduce thus eliminating the possibility of die crack defect. Another advantage will be the anchoring effect of the grooved area for thin die plus glue die attach process which will ensure the applicability of glue from the die backside towards the side of the die.

Fig. 3. Wafer Preparation Subtractive Method

Bryan Christian S. Bacquian "Die Backside Surface Subtractive Method for Thin Die Application," International Research Journal of Advanced Engineering and Science, Volume 4, Issue 3, pp. 318-320, 2019.

# III. CONCLUSION

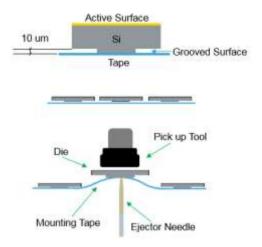

The innovative solution offers the process improvement for thin die attach eliminating die crack phenomena during pick step caused by high stress of mounting tape adhesion strength (Figure 4). Several advantages have been offered like elimination of die crack related defects, it broaden the application of thin die ad will increase the process capability of die attach machine. Finally, the process have offer unique process methodology using the existing process and go beyond the well-known process.

Fig. 4. Die Attach Pick mechanism using Subtractive Method Process

### REFERENCES

- Sandireddy, S., Jiang, T., Advanced Wafer Thinning Technologies to Enable Multichip Packages, Institute of Electrical and Electronics Engineers 2005

- [2] Chia, L.C., Huat, L.B., Wan, C.M., Robiatum, S.S., Man, J.L.S, Characterization of Silicon Die Strength with Different Die Backside Unevenness Location, 38th International Electronic Manufacturing Technology Conference, 2018

- [3] Sung A. N., Ratnam, M., Loh, W.P., Simulation of surface roughness and topography in finish turning using digital image subtraction, Institute of Electrical and Electronics Engineers 2011

- [4] Chin, WL, Tan, CE., Shauffi, N., Crack Die Elimination by Comprehensive Optimization throughout All Assembly Process Steps, 37th International Electronic Manufacturing Technology Conference, 2016

- [5] Stöckli, T., Rodriguez, I., Ernst, U., Harnisch, O., Thin Die Novel Process for Stack Die Packages and Yield Optimization, Kulicke and Soffa Industries Inc