# Conditional Capturing System for Low Power Clock Distribution Networks

C. Sasikala<sup>1</sup>, P. Ramalakshmi<sup>2</sup>

<sup>1, 2</sup>Electronics and Communication Engineering, Anna University, Coimbatore, Tamil Nadu, India-641109 Email address: <sup>1</sup>sasiece181932gmail.com

Abstract—Low-power design is becoming a crucial design objective due to the growing demand on portable applications and increasing difficulties in cooling and heat removal. A clock distribution network (CDN) delivers the clock signal which act as a reference to all sequential elements in the synchronous systems. The clock distribution network consumes a considerable amount of power in electronic devices. The proposed conditional capturing method for clock distribution using current is used to distribute a global clock. Further a pulsed logic is adapted to reduce the power consumption. This method solves the timing problem between pulsed latches through the use of multiple non-overlap delayed pulsed clock signals. When the CMPFFE is combined with pulsed logic, the design results in lower average power compared to traditional voltage mode clocks.

**Keywords**— CMPFFE, current mode, low power clock distribution, pulse logic, skew.

# I. INTRODUCTION

#### Low Power VLSI

The advantage of utilizing a combination of low-power components in conjunction with low-power design techniques is more valuable now than ever before. Requirements for lower power consumption continue to increase significantly as components become battery-powered, smaller and require more functionality. In the past the major concerns for the VLSI designers was area, performance and cost. Power consideration was the secondary concerned. Now a day's power is the primary concerned due to the remarkable growth and success in the field of personal computing devices and wireless communication system.

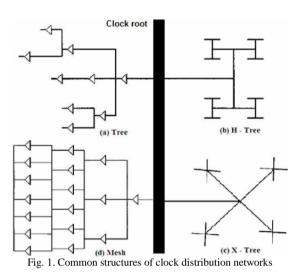

## Clock Distribution Network

The clock distribution network in digital integrated circuits distributes the clock signal which acts as a timing reference controlling data flow within the system. Since the clock signal has highest capacitance and operates at high frequencies, the clock distribution network consumes a large amount of total power in synchronous system. The main objectives in the design of CDNs are to minimize skew, jitter, and power. Clock skew is defined as the difference in the arrival time of the clock edges at different locations in the CDN. Skew is mainly caused by variations between clock buffers, interconnect widths, and loading at different clock paths. Clock jitter is defined as the difference in the arrival time of the clock edge at the same location in the CDN.

Clock Distribution Network Structures

#### II. RELATED WORKS

A various papers which are essential to know the previously available techniques and their significance and limitations. These papers describe various methods to increase the throughput. The area and power consumption overhead coming from these methods are discussed here

Riadul Islam and Matthew R. Guthaus, "Low-Power Clock Distribution Using a Current-Pulsed Clocked Flip-Flop", IEEE transactions on circuits and systems-I: regular papers, vol. 62, no. 4, April 2015[9]. In this paper the implemented CDN network that uses current instead of voltage. The high performance current mode pulsed flip flop with enable (CMPFFE) is combined with the CM transmitter. It is also used for the one to many clock distribution networks. CDN exhibits 62% lower average power. The CMPFFE uses an input current-comparator (CC) stage, a register stage, and a static storage cell. The CC stage compares the in put push pull current with a reference current and conditionally amplifies the clock to a full-swing voltage pulse that triggers the data to latch at the register stage. If the resistance of wire to high means, it will affect the performance of the CMPFFEs.

Riadul Islam, Matthew R. Guthaus, "Current-mode clock distribution" in Proc.ISCAS, Jun. 2014, pp. 1203–1206[10]. In this paper the clock distribution that use current rather than voltage .One to many clock distribution network is used. To accomplish this, a new high-performance current-mode pulsed flip-flop (CMPFF) using 45 nm CMOS technology. The high performance current mode pulsed flip flop (CMPFF) is combined with the CM transmitter. In CMPFF method there is

International Research Journal of Advanced Engineering and Science

ISSN: 2455-9024

no enable signal is used. It consumes high power compared with clock distribution using a CMPFFE.

Byung-Do Yang "Low-power and area-efficient shift register using pulsed latches" IEEE transactions on circuits and systems—I: regular papers, vol. 62, no. 6, June 2015[2]. In this paper he proposes a low-power and area-efficient shift register using pulsed latches. The area and power consumption are reduced by replacing flip-flops with pulsed latches. The shift register uses a small number of the pulsed clock signals by grouping the latches to several sub shifter registers and using additional temporary storage latches. A master-slave flip-flop using two latches can be replaced by a pulsed latch consisting of a latch and a pulsed clock signal. All pulsed latches share the pulse generation circuit for the pulsed clock signal. As a result, the area and power consumption of the pulsed latch become almost half of those of the master-slave flip-flop. This shift register saves 37% area and 44% power compared to the conventional shift register with flip-flops.

M. Dave, M. Jain, S. Baghini, and D. Sharma, "A variation tolerant current-mode signaling scheme for on-chip interconnects," IEEE Trans.Very Large Scale Integr.(VLSI) Syst., vol. PP, no. 99, pp. 1–12, Jan.2012[6]. In this paper they propose a variation tolerant dynamic overdriving CMS scheme. Variation tolerant CM scheme including Rx and Tx circuits and the inverter amplifier Rx circuit provides low-impedance to ground and holds the terminal point at the switching threshold. However, this comes at the expense of large static and dynamic power when compared to the other CM techniques and makes it unattractive compared to existing VM signaling.

Y.-T. Hwang, J.-F. Lin, and M. hwa Sheu, "Low-power pulse-triggered flip-flop design with conditional pulseenhancement scheme," IEEE Trans.Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 2, pp.361–366, Feb. 2012[11]. In this paper a novel low-power pulse-triggered flip-flop (FF) design is presented. A simple two-transistor and gate design is used to reduce the circuit complexity. Second, a conditional pulse-enhancement technique is devised to speed up the discharge along the critical path only when needed. As a result transistor sizes in delay inverter and pulse-generation circuit can be reduced for power saving. Maximum power saving against rival designs is up to 38.4%.

# III. PROPOSED BLOCK DIAGRAM

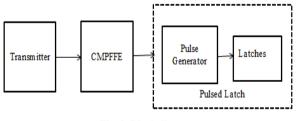

The proposed block diagram for the conditional capturing system is shown in figure 2. The block diagram consists of a three blocks. There are current mode transmitter, current mode pulsed flip flop with enable and a pulsed latches.

Fig. 2. Block diagram

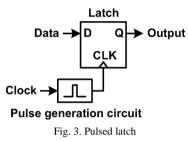

# IV. PULSE LOGIC

In a pulsed logic a latch synchronized by a pulse clock which is called pulsed latch. A pulsed latch can be approximated as a fast, lower power, and small FF. A pulsed latch consisting of a latch and a pulsed clock signal shown in figure 3. All pulsed latches share the pulse generation circuit for the pulsed clock signal. By using the pulsed latch the pulse distortion and clock skew can be well controlled. As a result, the area and power consumption of the pulsed latch become almost half. The pulsed latch is an attractive solution for small area and low power consumption.

In the conventional delayed pulsed clock circuits, the clock pulse width must be larger than the summation of the rising and falling times in all inverters in the delay circuits to keep the shape of the pulsed clock. However, in the delayed pulsed clock generator in figure 6 the clock pulsed width can be shorter than the summation of the rising and falling times because each sharp pulsed clock signal is generated from an AND gate and two delayed signals. Therefore, the delayed pulsed clock generator is suitable for short pulsed clock signals.

### V. CURRENT MODE TRANSMITTER

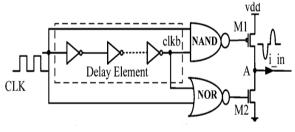

In order to integrate the CMPFFE, a Tx provides a push pull current into the clock network and distributes the required amount of current to each CMPFFE. The Tx receives a traditional voltage CLK from a PLL/clock divider at the root of the H-tree network and supplies a pulsed current to the interconnect which is held at a near constant voltage. The clock distribution is a symmetric H-tree with equal impedances in each branch so that current is distributed equal to each CMPFFE leaf node.

Fig. 4. Current mode transmitter

The pulsed current Tx is shown in figure 4. The NAND gate uses the CLK signal and a delayed inverted CLK signal, clkb, as inputs to generate a small negative pulse to briefly turn on M1. Hence, the PMOS transistor briefly sources charge from the supply while the NMOS is off. Similarly, the

C. Sasikala and P. Ramalakshmi, "Conditional capturing system for low power clock distribution networks," *International Research Journal of Advanced Engineering and Science*, Volume 1, Issue 2, pp. 135-138, 2016.

NOR gate utilizes the negative edge of the CLK and clkb signals to briefly turn on M2. Hence, the NMOS transistor briefly sinks current while the M1 is off. The non-overlapping input signals from the NAND-NOR gates remove any short circuit current from Tx.

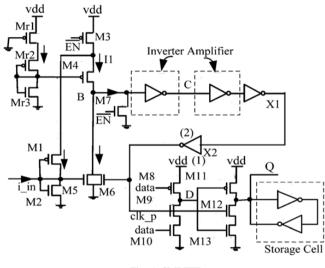

### VI. CMPFFE

The CMPFFE uses an input current-comparator (CC) stage, a register stage, and a static storage cell. The CC stage compares the input push pull current with a reference current and conditionally amplifies the clock to a full-swing voltage pulse that triggers the data to latch at the register stage. The feedback pulsed FF is in stark contrast to the previous CM schemes which utilized expensive Rx circuits and buffers to drive the final FFs.

# Fig. 5. CMPFFE

# VII. PROPOSED SYSTEM

#### Conditional Capturing System

A conditional capturing system is a proposed system for the low power clock distribution networks. A conditional capturing system uses a current mode transmitter. The current mode pulsed flip flop with enable is used in the conditional capturing system enhancement. There is a pulsed logic technique is used to transmit the clock signal as a pulsed clock to get an output. In a pulsed logic a latch synchronized by a pulse clock which is called pulsed latch. A pulsed latch is consisting of a latch and a pulsed clock signal which is generated by a pulse generator. All pulsed latches share the pulse generation circuit for the pulsed clock signal.

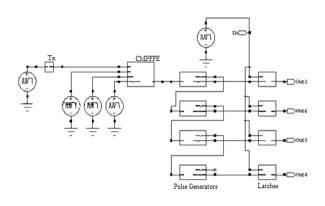

#### Proposed Circuit Diagram

The figure 6 shows the proposed conditional capturing system's circuit diagram. The given input signal is transmitted through the transmitter circuit. The transmitter circuit is interconnected with the CMPFFE circuit.

The signal is amplified and transfer through the pulse generator circuit. And also the latch receives the amplified signal and gives the output with reduced skew rate. By using this circuit the power is consumed in the clock distribution networks.

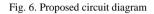

Schematic View

Fig. 7. S-Edit window showing the schematic view

The figure 7 shows that the S-Edit window of the conditional capturing system.

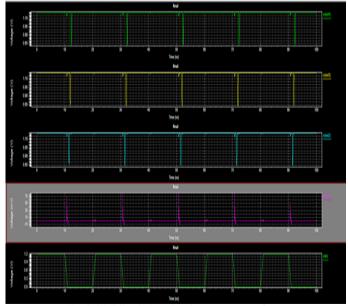

Output Waveform

Fig. 8. W-Edit window showing output wave form

C. Sasikala and P. Ramalakshmi, "Conditional capturing system for low power clock distribution networks," *International Research Journal of Advanced Engineering and Science*, Volume 1, Issue 2, pp. 135-138, 2016.

In figure 8 the W-Edit window showing the output wave forms of the proposed system. In the wave form analysis the input wave form is transmitted through the pulsed latch and gives the clock signal as the pulses.

## VIII. CONCLUSION

By using the pulsed logic technique the conditional capturing system is designed and simulated which is used in the Clock Distribution Networks (CDNs). The power consumption result of the conditional capturing system is compared with the existing system. The power consumption is reduced and the clock signal is amplified with reduced skew rate. The designs are designed and simulated by using the Tanner EDA tool.

#### REFERENCES

- A. Narasimhan, S. Divekar, P. Elakkumanan, and R. Sridhar, "A lowpower current-mode clock distribution scheme for multi-GHz NoCbased SoCs," 18<sup>th</sup> International Conference on VLSI Design held jointly with 4<sup>th</sup> International Conference on Embedded Systems Design, pp. 130–133, 2005.

- [2] B.-Do Yang "Low-power and area-efficient shift register using pulsed latches" *IEEE transactions on Circuits and Systems—I: regular papers*, vol. 62, issue 6, pp. 1564-1571, 2015.

- [3] E. Consoli, M. Alioto, G. Palumbo, and J. Rabaey, "Conditional pushpull pulsed latch with 726 fJops energy delay product in 65 nm CMOS," *IEEE International Solid-State Circuits Conference*, pp. 482–484, 2012.

- [4] H. Zhang, G. Varghese, and J. M. Rabaey, "Low swing on-chip signaling techniques: Effectiveness and robustness," *IEEE Transactions* on Very Large Scale Integration (VLSI) Systems, vol. 8, issue 3, pp. 264–272, 2000.

- [5] K. Absel, L. Manuel, and R. Kavitha, "Low-power dual dynamic node pulsed hybrid flip-flop featuring efficient embedded logic," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 21, no. 9, pp. 1693–1704, 2013.

- [6] M. Dave, M. Jain, M. S. Baghini, and D. Sharma, "A variation tolerant current-mode signaling scheme for on-chip interconnects," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 21, issue 2, pp. 342-353, 2012.

- [7] M. A. El-Moursy and E. G. Friedman, "Exponentially tapered h-tree clock distribution networks," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 13, issue 8, pp. 971–975, 2005.

- [8] N. K. Kancharapu, M. Dave, V. Masimukkula, M. S. Baghini, and D.K. Sharma, "A low-power low-skew current-mode clock distribution network in 90nm CMOS technology," *IEEE Computer Society Annual Symposium on VLSI*, pp. 132–137, 2011.

- [9] R. Islam and M. R. Guthaus, "Low-power clock distribution using a current-pulsed clocked flip-flop," *IEEE Transactions on Circuits and Systems—I: Regular Papers*, vol. 62, issue 4, pp. 1156–1164, 2015.

- [10] R. Islam and M. R. Guthaus, "Current-mode clock distribution," *IEEE International Symposium on Circuits and Systems (ISCAS)*, pp. 1203–1206, 2014.

- [11] Y.-T. Hwang, J.-F. Lin, and M. Hwa Sheu, "Low-power pulse-triggered flip-flop design with conditional pulse-enhancement scheme," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 20, issue 2, pp. 361–366, 2012.